Block Diagram 8255 42+ Images Result

Block Diagram 8255. For bsr mode always d7 will be 0. Also explain different operating modes of 8255.

Package sizes are not to scale. The read/write control logic manages all of the internal and external transfers of both data and control words. For bsr mode always d7 will be 0.

porsche 964 turbo wiring diagram chapman security system wiring diagram 2007 chevy aveo fuse box diagram yamaha 703 wiring diagram

8255 Programmable Peripheral Interface YouTube

It can be used with almost any microprocessor. Bus interface unit (biu) 2. The 8255a is a general purpose programmable i/o device designed to transfer the data from i/o to interrupt i/o under certain conditions as required. Block diagram of intel 8254.

Source: youtube.com

8255 block diagram ei omectionm data 60s » e. Block diagram and pin diagram of 8255: For operating modes of 8255 refer q6 *** 1. This is economical, functional, flexible but is a little complex and general purpose i/o device that can be used with almost any microprocessor. Block diagram of intel 8086 the 8086 cpu is divided into two.

Source: mediatoget.blogspot.com

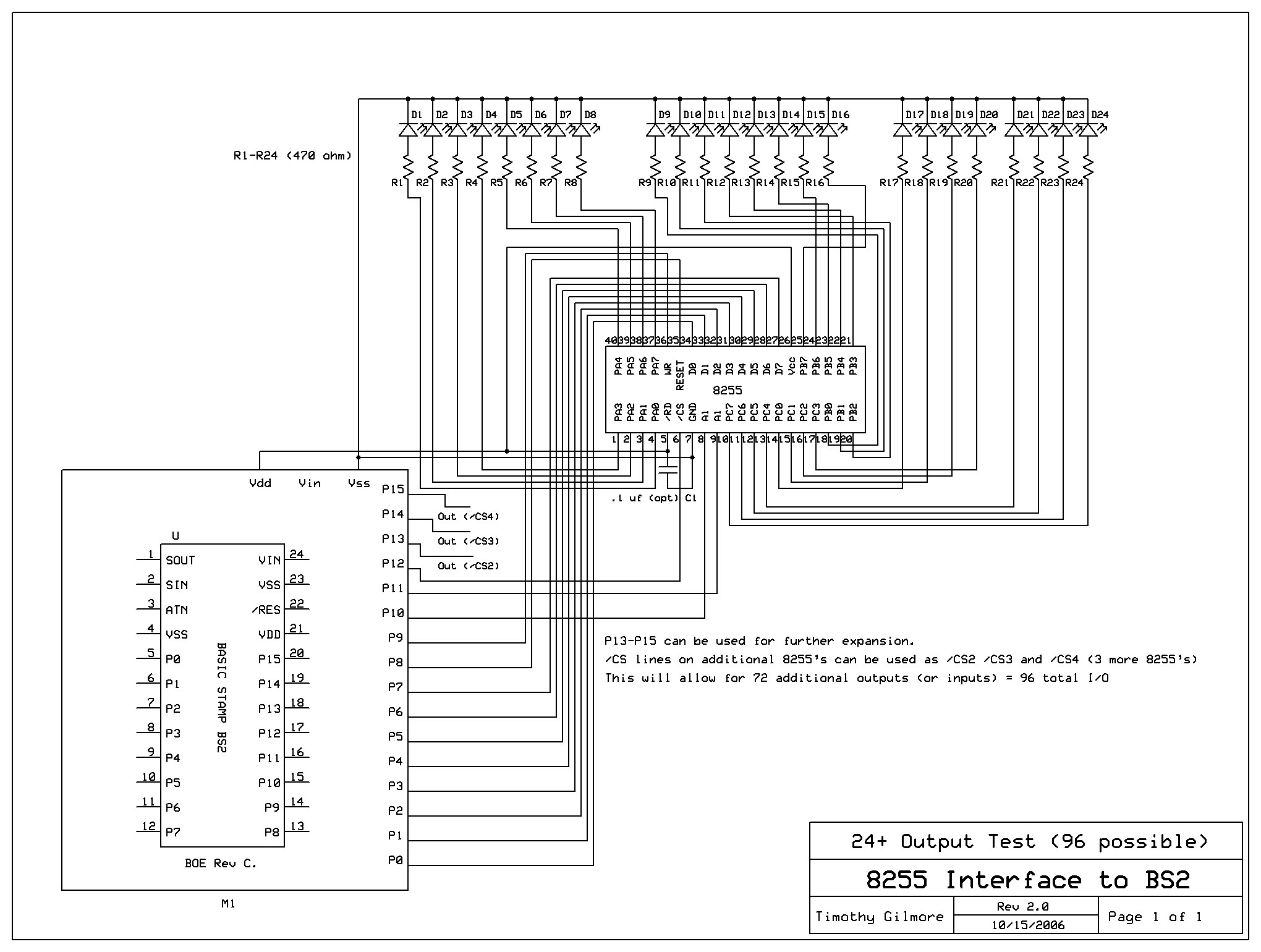

Figure shows the internal block diagram of 8255a. Determine the content of the control register and program the 8255 to get data from port b and send it to both port a and port c. We will study the complete ic structure of it, and will also study the functionalities that are performed by each of the pins. The 8255a.

Source: slideserve.com

In this article, we are going to study the pin diagram of the 8255 ppi (programmable peripheral interface). 2 pin diagram of 8255. Block diagram of intel 8086 features of 8086 microprocessor: Bit set reset (bsr) mode. —ports a, b, and c can be individually programmed as input or output ports.

Source: mobiparadise.mobi

Package sizes are not to scale. Block diagram of 8255 (architecture) ( cont.) • it has a 40 pins of 4 groups. Block diagram of the 8255. The 8255 has 24 i/o pins divided into 3 groups of 8 pins each. The control register is looking like this:

Source: slideserve.com

It can be used with almost any microprocessor. Determine the content of the control register and program the 8255 to get data from port b and send it to both port a and port c. Parallel communication interface and functional block diagram. Block diagram of intel 8086 the 8086 cpu is divided into two independent functional units: What is the.

Source: technobyte.org

2102440 introduction to microprocessors 6 8255 port selection 0 1 0 port c 0 1 1 control register 1 x x 8255 is not selected The intel 8255 (or i8255) programmable. Bus interface unit (biu) 2. The groups are denoted by port a, port b and port c respectively. Draw the block diagram of an 8255 ppi chip and describe.

Source: slideshare.net

It can be used with almost any microprocessor. There are two different modes of 8255. The 8255 has 24 i/o pins divided into 3 groups of 8 pins each. Block diagram and internal structure of 8255. •the internal block diagram and the pin configuration of 8255 are shown in fig.

Source: researchgate.net

Determine the content of the control register and program the 8255 to get data from port b and send it to both port a and port c. Block diagram of adc 0808/0809 The read/write control logic manages all of the internal and external transfers of both data and control words. In this video lecture i explained about block diagram (internal.

Source: webanalytik.info

Submitted by monika sharma, on august 16, 2019 the following is the internal structure of the 8255 ic, The read/write control logic manages all of the internal and external transfers of both data and control words. Also explain different operating modes of 8255. —ports a, b, and c can be individually programmed as input or output ports. Parallel communication interface.

Source: audioservicemanuals.com

Block diagram of 8255 (architecture) ( cont.) • it has a 40 pins of 4 groups. Mode 0, mode 1, and mode 2 fig 4.3 control word register bit format of 8255 for i/o mode and bsr mode. It is general purpose programmable parallel i/o device. Block diagram of intel 8254. Let’s break down the functionality of each block.

Source: ceae.info

The 8255a is a general purpose programmable i/o device designed to transfer the data from i/o to interrupt i/o under certain conditions as required. This is economical, functional, flexible but is a little complex and general purpose i/o device that can be used with almost any microprocessor. Package sizes are not to scale. Block diagram of 8255 (architecture) ( cont.).

Source: mediatoget.blogspot.in

Mode 0, mode 1, and mode 2 fig 4.3 control word register bit format of 8255 for i/o mode and bsr mode. This is economical, functional, flexible but is a little complex and general purpose i/o device that can be used with almost any microprocessor. It has 2 inputs namely clock and gate. The signal description of 8255 are briefly.

Source: vdocuments.mx

This is economical, functional, flexible but is a little complex and general purpose i/o device that can be used with almost any microprocessor. We will study the complete ic structure of it, and will also study the functionalities that are performed by each of the pins. —ports a, b, and c can be individually programmed as input or output ports..

Source: slideserve.com

2 pin diagram of 8255. • rd, wr , a 1, a 0 and reset are the inputs provided by the microprocessor to the read/ write control logic. Port a, b and c • data bus buffer: The figure down below shows the functional block diagram of 8254 timer: Let’s break down the functionality of each block.

Source: expaworld.blogspot.com

Mode 0, mode 1, and mode 2 fig 4.3 control word register bit format of 8255 for i/o mode and bsr mode. • rd, wr , a 1, a 0 and reset are the inputs provided by the microprocessor to the read/ write control logic. Block diagram and pin diagram of 8255: The 8255 has 24 i/o pins divided into.

Source: youtube.com

The read/write control logic manages all of the internal and external transfers of both data and control words. Port a as output, b as input, and all the bits in port c as output. This is a tristate bidirectional buffer used to interface the 8255 to system databus. Block diagram and internal structure of 8255. Draw the block diagram of.

Source: expaworld.blogspot.com

Group a and group b controls 4. Also explain different operating modes of 8255. In this video lecture i explained about block diagram (internal architecture )of 8255 ppi (programmable peripheral interface ) in hindi.in my next coming v. The signal description of 8255 are briefly presented as follows: 2102440 introduction to microprocessors 6 8255 port selection 0 1 0 port.

Source: 77.bloxhuette.de

Block diagram and internal structure of 8255. Data is transmitted or received by the buffer on execution of This is a tristate bidirectional buffer used to interface the 8255 to system databus. Q5) draw and explain the block diagram of 8255. Fig 4.2 8255 pin diagram 8255 has three operation modes:

Source: slideserve.com

The 8255a is a general purpose programmable i/o device designed to transfer the data from i/o to interrupt i/o under certain conditions as required. —ports a, b, and c can be individually programmed as input or output ports. Block diagram of intel 8086 the 8086 cpu is divided into two independent functional units: The read/write control logic manages all of.

Source: 8085microprocessorandapplications.blogspot.com

Figure shows the internal block diagram of 8255a. Block diagram and internal structure of 8255. Block diagram of intel 8086 the 8086 cpu is divided into two independent functional units: 8255 is a programmable peripheral interface i.e. Bit set reset (bsr) mode.